ADVERTISEMENT

早些時候,Intel在 Hot Chips 34 大會期間,介紹了與下一代 CPU 有關的一些關鍵細節。可知 14 代 Meteor Lake、15 代 Arrow Lake 和 16 代 Lunar Lake 將採用的 3D Foveros 封裝技術,很有樂高積木的風格。

據了解,Foveros 是一種先進的晶片間封裝技術,並且細分為三種。

- 首先是適用於量產的 Foveros 標準設計,其凸點間距在 50-25 μm,密度 > 400-1600/m㎡,功率 0.156 pJ/bit 。

- 其次是 Foveros Omni 設計,其旨在匹配連接基礎晶片複合體中的瓦片,提供高達 EMIB 四倍的互連凸點密度 —— 凸點間距 25 μm、密度 1600 / m㎡、功率 < 0.15 pJ/bit 。

- 然後是 Foveros Direct 設計,其提供 16 倍互連密度,具有更低延遲、更高頻寬、以及更低的功率 / 裸片要求 —— 凸點間距 < 10 μm、密度 > 10000 m㎡、功率 < 0.05 pJ/bit 。

在 12 代 Alder Lake 與 13 代 Raptor Lake CPU 率先採用了混合式核心架構設計之後,Intel還計畫利用 3D Foveros 封裝迎接多晶片時代。

14 代 Meteor Lake、15 代 Meteor Lake 和 16 代 Lunar Lake CPU 的特色有:

- Intel 下一代 3D 客戶端平台;

- 具有 CPU、GPU、SOC 和 IO 區塊的分解式結構;

- 採用 Foveros 互連的 Meteor / Arrow Lake 基礎區塊;

- 擁抱開放式的 UCIe 通用小晶片互連生態系統。

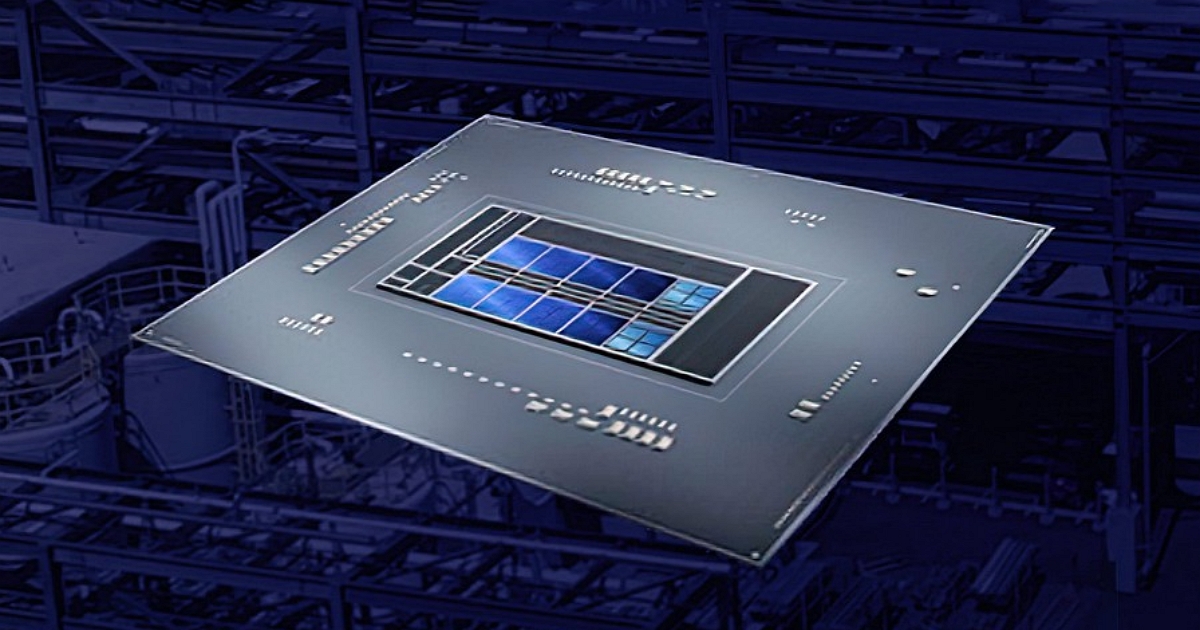

先說 Meteor Lake,該公司展示了一種全新的晶片布局,讓我們更好地瞭解了具有各種 IP 區塊的小晶片,主要拆分為 CPU、圖形區塊、單晶片系統、以及 IOE 區塊。

其中主 CPU 區塊將採用 Intel 4(7nm EUV)工藝節點,而 SoC 與 IOE 小晶片採用了台積電 6nm 工藝(N6)製造。

Intel宣稱 Meteor Lake 是其邁入小晶片生態的第一步,但據業內人士所述,情況並非如此,稱 Meteor Lake 的 tGPU 一直定的台積電 5nm(N5)設計。

運算圖區塊可在各種核心數量、世代、節點與快取之間完全擴展,且Intel不僅能夠在 Foveros 3D 封裝 CPU(如 Meteor Lake)中混搭不同核心架構、還可向上或向下擴展至不同節點。

圖形區塊也是如此,Intel可根據不同的核心、節點和快取規模進行縮放。圖表中的 tGPU 從 4~12 個 Xe 核心(64~192 EU)不等,但同一照片似乎也展示了 8 Xe / 128 EU 的版本。

SoC區塊亦可根據 SKU 放大或縮小,主要模組是低功耗 IP(特指 VPU)、SRAM、IO 和可擴展電壓設計。最後是 I/O 擴展區塊,其在通道數量、頻寬、協議和速率等方面,都是完全可擴展的。

接著,Intel展示了如何將各 IP 區塊排列到一起。金屬化的頂背,也是 Foveros 無源晶片所在的位置,正下方就是上述各個小晶片區塊。

這些瓦片之間透過 36 μm 間距(晶片-晶片)互連方案,與基礎區塊完成連接。Base Tile 帶有大電容,輔以 IO / 供電 / D2D 路徑的金屬層。

每個金屬層都是模組化的設計,帶有用於邏輯 / 儲存器的有源矽片。頂部和底部具有用於頂 / 底層互連的封裝凸點。

示例中的晶片,採用了 6P+8E 的混合式架構設計。另有 CPU / IOE 區塊,且通向 SOC 區塊的圖形區塊之間有兩個 Die-To-Die 連接。

作為 Foveros 3D 封裝的一部分,Intel表示在主小晶片頂部有一個無源中介層,其基於Intel自家的 22nm(FFL)工藝製造。

現階段它並沒有被分配任何用途,Meteor Lake CPU 也暫時用不到 EMIB 技術。但該公司計畫在未來使用更先進的封裝技術,並將之換成有源小晶片。

Foveros 晶片互連(FDI)的技術特點如下:

- 低壓 CMOS 介面;

- 高頻寬、低延遲;

- 支援同步與非同步信令;

- 低面積開銷;

- 2 GHz 主頻下的操作功耗在 0.15-0.3 pJ/bit 左右。

CPU 與 SOC 之間的互連,具有大約 2K(2×IDI)的主頻寬,圖形與 SOC 區塊也具有大約 2K(2×iCXL)的互連主頻寬,而 SOC 和 IOE 區塊則在 1K(IOSF,4×DisplayPort)左右。

不過 Meteor Lake CPU 的另一關鍵改進,就是提升了最大睿頻性能。得益於 Intel 4 技術的協同最佳化,其有望帶來較 Alder Lake CPU 更高的睿頻潛力,且 Base Tile 的總電流達到了 500 。

I/O 能力方面,Intel搬出了 Haswell 來比較。成本方面,隨著新一代晶圓成本的上漲,開發單晶片將變得更加不划算。

若Intel堅持按老方法造新晶片,其實也不是不可以。畢竟新製程節點不是擺設,只是難以將成本壓低到合理水準。

該公司稱,與單片式晶片製造方案相比,Meteor Lake 等分解式設計可提供更高的電晶體性能,以及跨各種工藝節點的更好 IP 更新速度和更高能效。

Intel透露,其 Meteor Lake SKU 的功耗設計從 <10W 到 >100W 不等,但採用小晶片設計的 CPU 性能仍與單片式設計相當。

此外該公司稱,14 代 Meteor Lake / 15 代 Arrow Lake CPU,確實正在走向桌上型和行動平台。

按照計畫,Intel計畫在 2023 / 2024 年發布 Meteor / Arrow Lake CPU,且兩者都採用下一代 LGA 1851 插槽。

至於 16 代 Lunar Lake CPU,據說該系列最初瞄向 15W 低功耗移動 CPU 細分市場,但鑑於距離正式上市還有幾年時間,我們仍不能排除未來有生變的可能。

最後,這並不是Intel首次在行動 / 部分桌面 SKU 之間劃出明確界限。除了歷史上的 Broadwell,近些年的 Ice Lake / Tiger Lake 系列也是如此。

請注意!留言要自負法律責任,相關案例層出不窮,請慎重發文!