ADVERTISEMENT

電腦晶片正式進入3D時代。

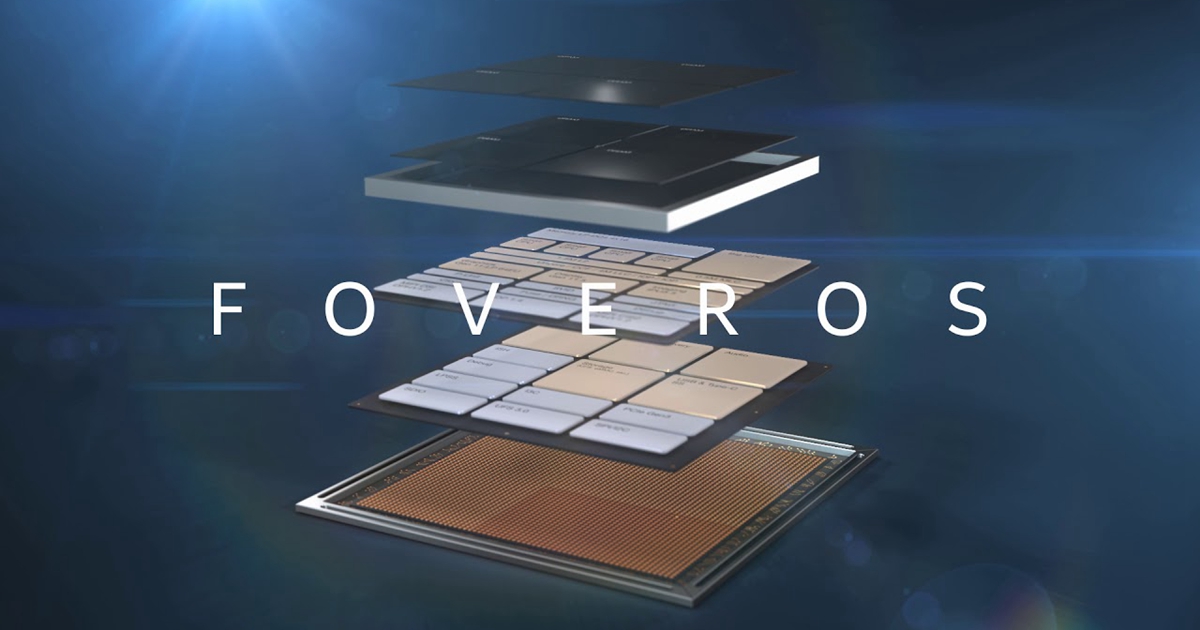

3D 堆疊晶片是Intel挑戰摩爾定律的新方向,它可以將晶片中的邏輯元件堆疊起來,大幅提升 CPU、GPU 及 AI 處理器的密度。在晶片製程工藝接近停滯的今天,或許只有這種方法才能繼續提高性能。

近日,Intel在半導體行業會議 Hot Chips 34 上展示了關於 3D Foveros 晶片設計的新細節,它將用於即將發布的 Meteor Lake、Arrow Lake 和 Lunar Lake 晶片。

最近有傳言稱,Intel的 Meteor Lake 將推遲上市,因為Intel的 GPU tile/chiplet 需要從 TSMC 3nm 節點切換到 5nm 節點。儘管Intel仍未分享有關它將用於 GPU 的特定節點的資訊,但公司代表表示,GPU 元件的計畫節點沒有改變,處理器有望在 2023 年按時發布。

值得注意的是,這一次Intel將只生產用於構建其 Meteor Lake 晶片的四種元件中的一種(CPU 部分)——台積電將生產另外三種。業內消息人士指出,GPU tile 是 TSMC N5(5nm 製程)。

Intel分享了 Meteor Lake 處理器的最新圖片,它將使用 Intel 4 行程節點(7nm 製程),首先投放市場的將是一款行動處理器,具有六個大核心跟兩個小核心。雖然Intel尚未證實,但該配置被認為分別是 Redwood Cove 和 Crestmont 架構。Meteor Lake 和 Arrow Lake 晶片覆蓋行動和桌上型電腦 市場的需求,而 Lunar Lake 將用於輕薄筆電,覆蓋功率 15W 及以下的市場。

封裝和互連的進步正在迅速改變現代處理器的面貌。兩者現在都與底層工藝節點技術一樣重要——並且可以說在某些方面更加重要。

Intel在本週一的許多披露都集中在其 3D Foveros 封裝技術上,它將用作面向消費市場的 Meteor Lake、Arrow Lake 和 Lunar Lake 處理器的基礎。這項技術讓Intel能把小晶片垂直堆疊在一個具有 Foveros 互連的統一基礎晶片上。Intel還將 Foveros 用於其 Ponte Vecchio 和 Rialto Bridge GPU 以及 Agilex FPGA,因此它可視為該公司若干下代產品的基礎技術。

Intel此前在其小批量的 Lakefield 處理器上把 3D Foveros 推向了市場,但 4 tile 的 Meteor Lake 和近 50 tile 的 Ponte Vecchio 才是該公司首個採用該技術大批量生產的晶片。在 Arrow Lake 之後,Intel將過渡到新的 UCIe 互連,進而進入使用標準化介面的小晶片(chiplet)生態系統。

Intel透露,它將把四個 Meteor Lake 小晶片(在Intel的語境稱為「瓦片 / tile」)放置在無源 Foveros 仲介層 / 基礎 tile 的頂部。小晶片和仲介層透過 TSV 連接連在一起,仲介層沒有任何邏輯。Meteor Lake 中的基礎 tile 與 Lakefield 中的不同,後者某種意義上可視為 SoC。3D Foveros 封裝技術還支援有源仲介層。Intel表示,它使用低成本和低功耗最佳化的 22FFL 工藝(與 Lakefield 相同)製造 Foveros 仲介層。Intel還為其代工服務提供了此節點的更新「Intel 16」變體,但尚不清楚Intel將使用哪個版本的 Meteor Lake 基礎 tile。

Intel將在此仲介層上安裝使用 Intel 4 行程的運算模組、I/O 塊、SoC 塊和圖形塊(tGPU)。所有這些單元都是Intel設計並採用Intel架構,但台積電將代工其中的 I/O、SoC 和 GPU 塊。這意味著Intel將只生產 CPU 和 Foveros 模組。

業內人士透漏,I/O die 和 SoC 是在台積電 N6 製程上製造的,而 tGPU 使用的是台積電 N5。(值得注意的是,Intel將 I/O tile 稱為「I/O Expander」,即 IOE)

Foveros 使用 36 微米的凸塊間距(互連密度的關鍵測量值),這是對 Lakefield 使用的 55 微米間距的改進。Foveros 路線圖上的未來節點包括 25 和 18 微米間距。Intel表示,理論上未來甚至可以使用混合鍵合互連(HBI)來達到 1 微米的凸塊間距。

成本一直是 3D 封裝晶片面臨的重要的問題之一,而 Foveros 將是Intel憑藉其領先封裝技術首次大批量生產。不過Intel卻表示,採用 3D Foveros 封裝生產的晶片與標準晶片設計相比具有極強的價格競爭力——在某些情況下甚至可能更便宜。

Intel將 Foveros 晶片設計為盡可能低成本,並且仍能實現公司提出的性能目標——它是 Meteor Lake 封裝中最便宜的晶片。Intel尚未共用 Foveros 互連 / 基礎 tile 的速度,但表示這些元件可以在無源配置中在「幾 GHz」上運行(該聲明暗示Intel已在開發的仲介層存在有源版本)。因此,Foveros 不需要設計者對頻寬或延遲限制妥協。

Intel還希望該設計在性能和成本方面都能很好地擴展,這意味著它可以為其他細分市場提供特化設計,或高性能版變體。

由於矽晶片工藝接近極限,每個電晶體的先進節點成本正呈指數級增長。而為較小的節點設計新的 IP 模組(如 I/O 介面)並不能為投資帶來太多回報。因此,在「足夠好」的現有節點上重新使用非關鍵 tile/chiplet 可以節省時間、成本和開發資源,更不用說簡化測試過程了。

對於單體晶片,Intel必須連續測試不同的晶片元素,例如記憶體或 PCIe 介面,這可能是一個耗時的過程。相比之下,晶片製造商也可以同時測試小晶片以節省時間。Foveros 在為特定 TDP 範圍設計晶片方面也具有優勢,因為設計者可以根據設計需要定制不同的小晶片。

這些觀點中的大多數聽起來很熟悉,它們都是 AMD 在 2017 年走上 chiplet 之路的相同因素。AMD 並不是第一個使用基於小晶片的設計的公司,但它是首先使用這種設計理念量產現代晶片的大廠,Intel在這方面似乎來的有點晚。不過,Intel提出的 3D 封裝技術遠比 AMD 基於有機仲介層的設計複雜得多,後者既有優點也有缺點。

這種差別最終將會在晶片成品中體現,Intel表示新款 3D 堆疊晶片 Meteor Lake 有望在 2023 年推出,Arrow Lake 和 Lunar Lake 將在 2024 年上市。

Intel還表示,Ponte Vecchio 超級電腦晶片將擁有超過 1000 億個電晶體,這款晶片預計將成為世界最快超級電腦 Aurora 的核心。

資料來源:

請注意!留言要自負法律責任,相關案例層出不窮,請慎重發文!