ADVERTISEMENT

Intel在2021架構日活動中除了發表家用處理器與顯示卡的資訊外,也帶來多款伺服器端的處理器、基處設施處理器、運算卡等產品資訊。

EMIB讓Xeon處理器如同疊積木

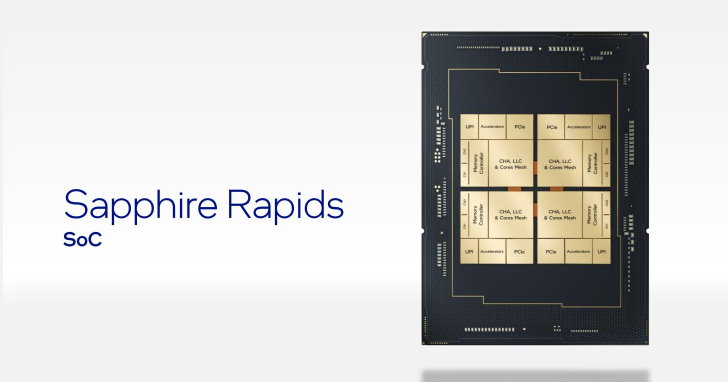

代號為Sapphire Rapids的下世代Intel Xeon可擴充處理器將採Intel 7製程製造,最大的特色就是用平舖的模組化SoC架構,並透過EMIB(嵌入式多晶片互連橋接)技術,在不耗損效能的情況下連接多個小晶片(Tile),能夠滿足不斷改變與增加的資料中心使用需求,為雲端、微服務和AI等彈性計算模型等應用提供充沛運算效能並為工作負載最佳化。

這樣的優勢除了能夠在設計過程中透過堆疊小晶片提升整體運算效能,也提供單一且平衡的統一記憶體存取架構,讓每條執行緒均可完全存取快取、記憶體和I/O等完整資源,達成SoC一致的低延遲和高頻寬資料傳輸。另一方面,由於SoC是由多個小晶片組合而成,所以當生產過程中有某個小晶片出現瑕疵,也只需廢棄該小晶片,而不用廢棄整個SoC,對良率的提升也有正面幫助。

IPU尬場DPU

Intel推出的基礎設施處理器(IPU)是款可程式化的網路裝置,能夠在雲端和通訊服務等應用情境分擔傳統CPU的運算負載,很明顯就是與NVIDIA的DPU相互競爭。

IPU具有下列多樣主要優勢:

- 基礎設施功能和承租戶(Tenant)工作負載之間的強分離,允許承租戶完全控制CPU

- 雲端營運商可以轉移基礎設施運算負載至IPU,最大化CPU使用率和收益

- IPU能夠管理儲存流量,於降低延遲的同時,亦可透過無碟伺服器架構有效率地使用儲存容量

為了因應不同應用情境,Intel推出多款規模不同的IPU滿足客戶多元且複雜的需求,其中包含首款ASIC IPU Mount Evans,以及採用Xeon D處理器和Agilex FPGA打造Oak Springs Canyon,此外還有Arrow Creek等產品。

伺服器運算卡也支援光線追蹤

Intel也在這次活動中發表了更多Xe HPC運算卡的資訊,它能提供領先業界的浮點運算效能與運算密度,加速AI、高效能運算(HPC)以及多種大數據分析的工作負載。

Xe HPC的架構與在前篇文章中提到的Xe HPG相似,其最基本的組成單元也是Xe Core,不過Xe HPC版本的配置為8組512 bit向量引擎,以及8組4096bit矩陣引擎,單一Xe Core運算能力比Xe HPG更高。

Xe Core配置對照表

Xe HPG(遊戲顯示卡):256 bit向量引擎 x 16 + 1024bit矩陣引擎 x 16

Xe HPC(高階運算卡):512 bit向量引擎 x 8 + 4096bit矩陣引擎 x 8

Xe HPC版本的Render Slice最多可以容納16個Xe Core(Xe HPG版本則為4個),而它也保留了數量為1:1的光線追蹤單元,因此每組Render Slice最多能夠擁有16個光線追蹤單元。根據Intel的說明,Xe HPC除了能應用於AI與數據運算外,也可以在專業繪圖領域發揮所長,因此保留光線追蹤功能。

而更高1層的單位為Stack,可由4個Xe HPC的Render Slice組成,每張運算卡可由2個Stack組成。筆者將Xe HPC運算卡的各階組成架構由大至小整理如下

Xe HPC運算卡組成架構(由大至小排列)

運算卡(最大的單位)

Stack(每張運算卡有2個Stack)

Render Slice(每個Stack有4個Render Slice)

Xe Core(每個Render Slice有16個Xe Core)

為了滿足Xe HPC運算卡之間的資料傳輸,Intel推出頻寬高達2TB/s的Xe Link匯流排提供GPU之間的連接性,讓8張運算卡能夠建立完全連接之拓撲,成為效能向上提升(Scale-Up)的成功關鍵。

採用Xe HPC微架構的Ponte Vecchio運算卡是目前世界上最複雜的晶片之一,它具有超過1000億個電晶體,並由5種不同製程的47種小晶片組成,其Render Slice具有8個Xe Core與合計4MB的L1快取記憶體,它除了透過EMIB技術整合小晶片,並實現低功耗的高速連結,還使用Foveros 3D堆疊封裝並透過高速MDFI互連能實現整合2個Stack的目標。

目前早期開發階段的Ponte Vecchio晶片已具有傑出的效能表現,於主流AI訓練與推論測試皆創下領先業界的紀錄。目前A0步進的晶片在FP32資料型態下具有超過45 TFLOPS效能,並有高於5 TB/s的記憶體交織結構頻寬與2 TB/s的連接頻寬。

在ResNet-50測試項目中,具有每秒可以處理超過3,400張照片的訓練效能,以及每秒超過43,000張照片的ResNet推論效能,高於競爭對手於2021年8月10日公布的效能數據。

Ponte Vecchio已成功過電開機,正處於驗證階段,並開始小量寄送樣品予客戶,預計於2022年推出至HPC和AI運算市場。

Intel執行長Pat Gelsinger提到:「我們正面臨望之生畏的運算挑戰,這些挑戰只能夠透過革命性的架構和平台去解決……Intel亟富才華的架構師和工程師們,讓這些技術成為可能。」世界正仰賴著架構師和工程師們解決最為困難的運算難題,以豐富人們的生活。這正是Intel為何加速執行我們的策略,因為我們的策略與執行正以極快的步伐,加速滿足這些需求。

系列文章:

Intel架構日活動表示自家處理器「大小核」架構,與Arm處理器的big.LITTLE架構並不完全相同

Intel於架構日說明Arc顯示卡硬體設計,不但有光追還有AI升頻

2021架構日點燃戰火,Intel伺服器CPU、GPU、IPU全面進攻(本文)

請注意!留言要自負法律責任,相關案例層出不窮,請慎重發文!